Technology

Senseeker's technology capabilities are ever expanding and evolving to enable our customers to produce the most advanced infrared imaging systems possible.

Digital readout ICs and digital pixel readout ICs (DPROICs) developed by Senseeker enable the newest generations of some of the world's highest performance infrared systems for every infrared band and for both passive and active imaging.

Advanced Digital Sensor Electronics and software supplied by Senseeker is used to evaluate and optimize FPA performance faster and reduce overall project cycle-time.

Senseeker Sensor Test Units (STUs) are established as the benchmark in lab equipment for focal plane array (FPA) testing and the STU product line is expanding to accommodate the largest format and highest data rate FPAs in the industry.

Integrated Circuits

Sensor Test Units

Electronics

Software

Ecosystem

Publications

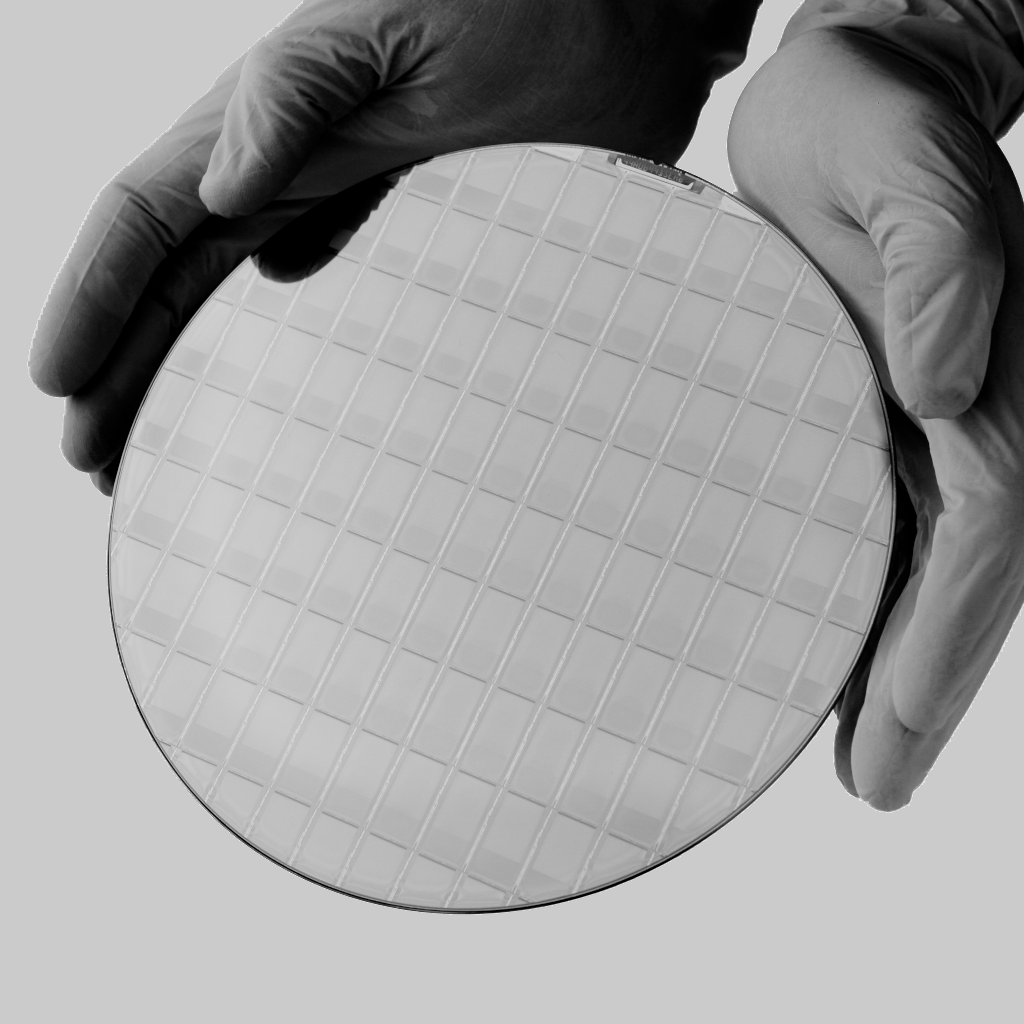

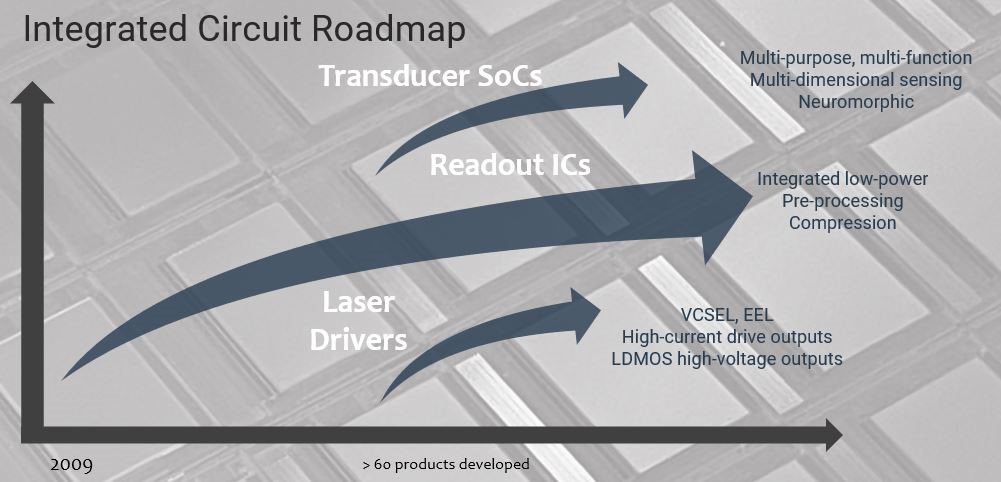

Integrated Circuits

Senseeker has a strong heritage in developing cutting-edge digital readout ICs and is working to advance the state-of-the-art in the largest formats, smallest pixel pitches and most advanced functionality. We have developed both large and small pixel active and active/passive DROICs. We have expanded the range of what a DROIC can do, bringing cutting edge technology to life in our hardware deliverables for our customers. Of particular note is Senseeker’s line of high dynamic range digital pixel readout ICs (DPROICs).

DPROICs offer vastly improved dynamic range and a welcome disconnect between sensitivity and maximum signal. No longer does the sensitivity have to worsen by the square root of the increase in well capacity, as is the case with conventional analog pixels. Instead, the maximum well capacity of a DPROIC can be increased independently by increasing the number of bits in each pixel.

Senseeker readouts are known for their useful operating modes and operating speed, including high-speed multi-window capability. Windows can be implemented to track small fast-moving targets at tens of thousands of frames per second. This capability is essential in advanced Infrared Search & Track (IRST) systems and Senseeker continues to advance this functionality to new levels of performance.

Senseeker leads the industry in small pixel designs and large formats. Senseeker’s portfolio of designs that are in production include a number of 5 µm pixel pitch digital readouts and a capability to produce even smaller pixel sizes. Format sizes of hundreds of Megapixels are possible using a proven stitched architecture methodology.

As well as industry-leading digital readout ICs, Senseeker has developed unique high-voltage and high-current laser driver ICs that complement our active pixel digital readout ICs. Senseeker IC technology is well suited to expanding out to other senses, seeking new ways to interact with the world around us with future multi-modal transducer integrated circuits.

Return to Top

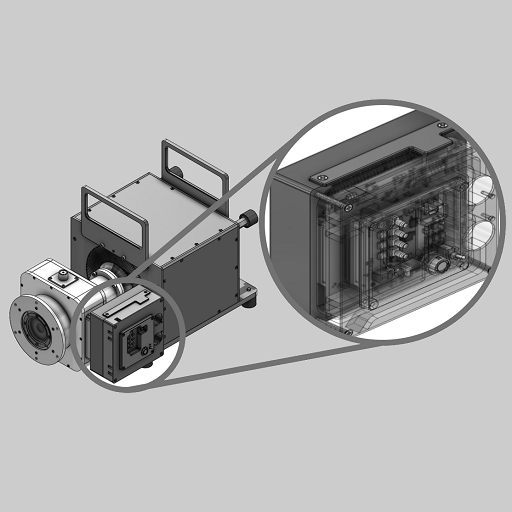

Sensor Test Units

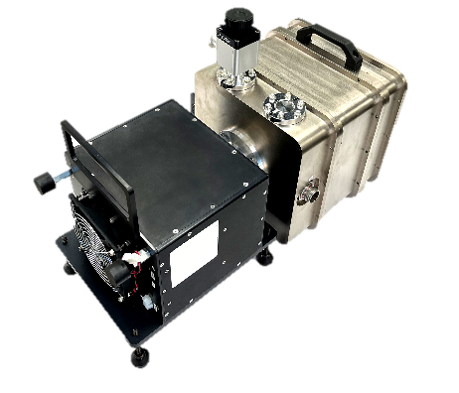

Senseeker has invested significantly in the evolution of our Sensor Test Unit (STU) product lines – LN2 pour-fill Dewars, Closed-cycle cryocooler STUs and Thermoelectric STUs that are capable of cold and hot operation from below 50 K to above 360 K (85°C).

An 'XL' model with a significantly larger vacuum enclosure has been developed to accommodate the largest FPAs that are currently under development or arrays of smaller FPAs for increasing test throughput. Large format FPAs and arrays of smaller FPAs have more electrical connections that must be accommodated and optimally routed in the larger form factor vacuum chamber and the XL STU provides that space and functionality.

To complement the STU products, Senseeker is developing further cryogenic test equipment for the fully-equipped infrared image sensing laboratory. A 12" integrating sphere with dedicated cryocooler will be available shortly. This 'Cryosphere' will enable FOD-free rapid testing of FPAs, by reducing vacuum and thermal cycling overhead when FPAs are changed in the STU that is connected to the output port.

Senseeker continues to invest in advanced products that simplify the process of bringing-up, testing and characterizing cooled or uncooled FPAs. Optimizing our portfolio of STUs and other associated FPA testing equipment is an ongoing process that allows us to stay aligned with customer requirements and the advanced capabilities of cutting-edge readout ICs that Senseeker pioneers.

Return to Top

Electronics

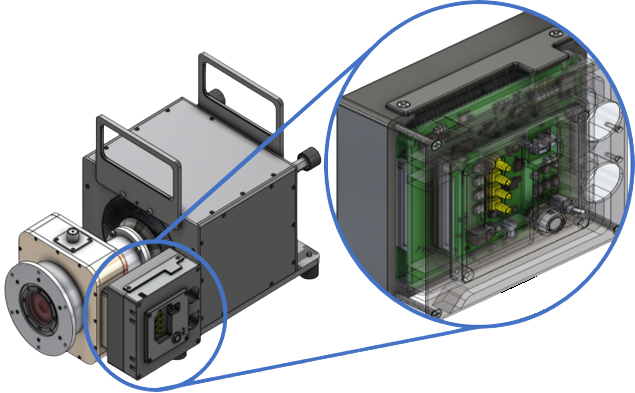

Senseeker Digital Sensor Electronics support advanced Senseeker digital readouts and digital pixel readout ICs. Senseeker can provide a range of capabilities from commercial grade through highly reconfigurable electronics systems that are built-to-order.

Digital Sensor Electronics that support Senseeker’s readout ICs is evolving to keep pace with the technological advances of the ROICs. This includes:

Senseeker engineered electronics are used for evaluation and characterization of all the new ICs that Senseeker designs. It has proven to be advantageous to Senseeker customers to have access to the same test equipment set (electronics and STUs) that is used in-house by Senseeker engineers. Senseeker offer customization options to this equipment in order to meet specific customer testing requirements.

Return to Top

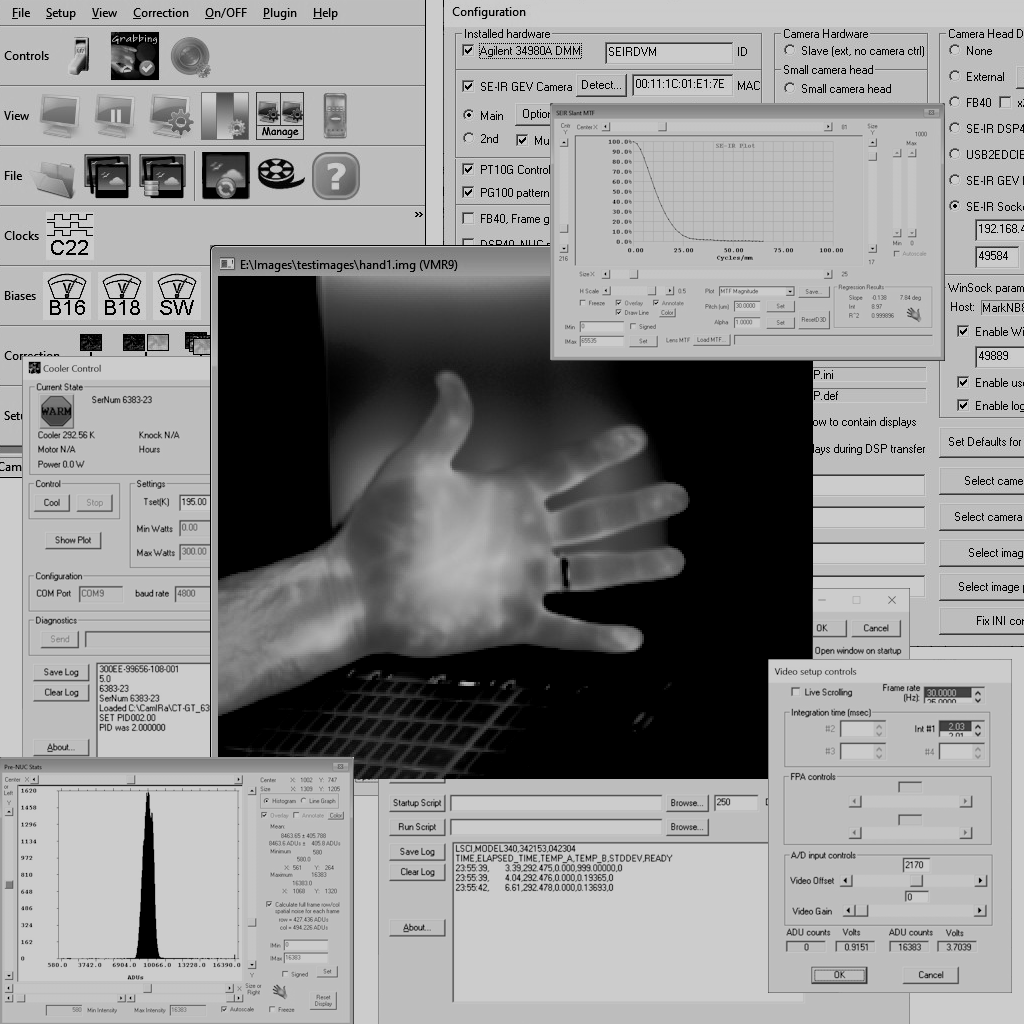

Software

Senseeker’s CamIRa

Senseeker's software capabilities will continue to evolve to maintain support for the newest readout ICs including larger format sizes and higher speeds possible in new generations of digital readouts.

Return to Top

Ecosystem

Senseeker's role in the infrared industry is to enable and simplify our customers development of FPAs. Senseeker does not manufacture FPAs, but we streamline our customers ability to do so by offering readout ICs and all of the test hardware, software and services that are required to get an FPA into production quickly and get the best imaging performance possible.

Senseeker has a wide range of industry ecosystem partners that offer complementary products and services that are required to implement infrared imaging systems. Senseeker often connects these partners with our customers to help facilitate system solutions more quickly. These partners include infrared detector developers, FPA developers, packaging suppliers and services providers, imaging stack electronics developers, subsystem, IDCA and camera core developers.

Senseeker's ecosystem will continue to evolve to encompass a network of specialist suppliers that can offer the associated products and services that support Senseeker's core portfolio. Many FPA suppliers offer products based upon Senseeker readout ICs. A select few of those who have provided their permission to disclose this fact include Attollo Engineering, Princeton Infrared Technologies, and QmagiQ. Arc Nano offers hybridization of Senseeker readout ICs along with other services.

Return to Top

Publications

Low-noise High-sensitivity Digital Readout Integrated Circuit for SWIR Imaging

T. Poonnen, S. McCotter, K. Esparza, B. Ratledge, W. Korth, N. Dhawan, and K. Veeder | Proceedings of SPIE Defense + Commercial Sensing Conference, 2024 | more info

Swarm Intelligent Readout Integrated Circuit Pixel Array for Advanced Infrared Search and Track

T. Poonnen, and W. Korth | Proceedings of SPIE Defense + Commercial Sensing Conference, 2024 | more info

Digital Pixel Readout Integrated Circuit for High Dynamic Range Infrared Imaging

T. Poonnen, N. Dhawan, W. Korth, and K. Veeder | Proceedings of SPIE Defense + Commercial Sensing Conference, 2023 | more info

Proximal Interpolation, Tone Mapping and Pseudo-Coloring for Intra-Frame High Dynamic Range Infrared Imaging

T. Poonnen, W. Korth, C. Peterson, and K. Veeder | Proceedings of SPIE Defense + Commercial Sensing Conference, 2022 | more info

Digital Readout Integrated Circuit for High Dynamic Range Infrared Imaging

T. Poonnen, S. McCotter, K. Esparza, and K. Veeder | Proceedings of SPIE Defense + Commercial Sensing Conference, 2021 | more info

Digital Converters for Image Sensors

K. Veeder | SPIE Press Book, ISBN: 9781628413892, 2015 | more info

Fundamentals of Infrared and Visible Detector Operation and Testing

J. D. Vincent, S. E. Hodges, J. Vampola, M. Stegall, and G. Pierce | Wiley, ISBN: 9781119011897, 2015 | more info

White Papers

Oxygen

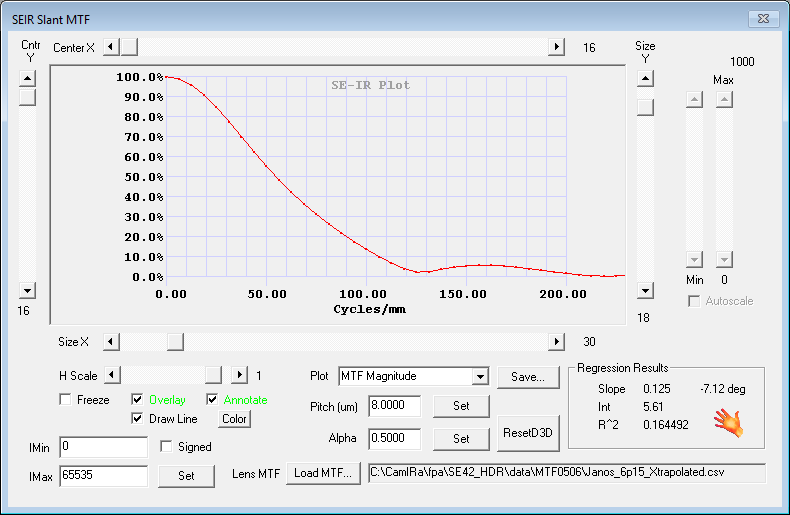

Intra-frame high dynamic range (HDR) infrared imaging is accomplished in a 1280 x 720 format, 8 μm pixel pitch digital readout integrated circuit (DROIC) by spatially combining neighboring pixels with different integration times to obtain HDR pixels. Intra-frame HDR imaging achieves the same level of dynamic range improvement as traditional inter-frame HDR imaging without compromising temporal resolution. Proximal interpolation to retain the spatial resolution of the HDR infrared frame, tone mapping to effectively display HDR infrared content on limited dynamic range displays, and pseudo-coloring to better visualize HDR infrared imagery are discussed.

Complete the form below to request a white paper:

Oxygen

A 1280 x 720 format, 8 µm pixel pitch digital readout integrated circuit (DROIC) for intra-frame high dynamic range (HDR) infrared imaging is presented. Unlike traditional inter-frame HDR imaging where frames with different integration times are temporally combined to obtain an HDR frame, intra-frame HDR imaging is accomplished by spatially interpolating neighboring pixels with different integration times to obtain HDR pixels, thereby achieving the same level of dynamic range improvement without compromising temporal resolution and mostly retaining spatial resolution. In intraframe HDR mode, the infrared imager can achieve a phenomenal >57 dB improvement in dynamic range over normal mode.

Complete the form below to request a white paper:

Calcium™ :: Digital Pixel Readout Integrated Circuit for High Dynamic Range Infrared Imaging

Digital pixels enable the disassociation of well capacity with noise floor. This allows for better sensitivity for small signals

and significantly increased well capacity for large signals. A 640 x 512 format, 20 µm pixel pitch digital pixel readout integrated circuit (DPROIC) for high dynamic range infrared imaging is presented. The architecture uses an extended counting approach that is optimized for low power consumption. This DPROIC boasts a programmable well capacity of 40 Me- in high gain (HG) and >400 Me- in low gain (LG) with no rollover. Read noise is 50 e- rms, HG, and 330 e- rms, LG, for integrate-then-read and 85 e- rms, HG, and 700 e- rms, LG, for integrate-while-read at 80 K. This readout, with LWIR SLS detectors, achieves single digit millikelvin noise-equivalent temperature difference.

Complete the form below to request a white paper:

Neon

Indium gallium arsenide and colloidal quantum dot SWIR sensors can produce stronger contrast imagery than their visible counterparts due to the reduced scattering in the SWIR band. A 640 x 512 format, 10 &mircro;m pixel pitch low-noise highsensitivity DROIC, with a capacitive transimpedance amplifier pixel front end, for SWIR imaging is presented. This DROIC has variable gain pixels with well capacities of approximately 22 ke- in high gain, 160 ke- in mid gain and 1.1 Me- in low gain. The readout boasts a low read noise of only 15 e- rms at room temperature in high gain with correlated double sampling. This DROIC can run at 700 fps full frame and 8.9 kfps for 32 x 32 window.

Complete the form below to request a white paper:

Return to Top